返回

返回

技術(shù)分享 | 晶圓級(jí)同步結(jié)構(gòu)化V型槽技術(shù):重塑高精度PIC光纖接口的未來(lái)

發(fā)布日期:2025-12-15

隨著光子集成電路(PIC)在數(shù)據(jù)中心與AI計(jì)算等領(lǐng)域的廣泛應(yīng)用,光纖與PIC的高精度耦合正成為提升系統(tǒng)性能及量產(chǎn)能力的關(guān)鍵挑戰(zhàn),也促使行業(yè)尋求更加先進(jìn)的技術(shù)解決方案。近日,專注于光通信與光子集成技術(shù)的國(guó)際知名媒體PIC Magazine發(fā)表了炬光科技專題文章《Reimagining PIC-fibre interfaces with engineered V-Groove technology (重塑高精度PIC光纖接口的未來(lái))》,深入探討了晶圓級(jí)同步結(jié)構(gòu)化V型槽技術(shù)如何在精度、產(chǎn)能、可靠性和可擴(kuò)展性上帶來(lái)結(jié)構(gòu)性突破,為光子集成封裝帶來(lái)更多創(chuàng)新與產(chǎn)業(yè)價(jià)值。

文章要點(diǎn)

PIC光纖接口的隱形瓶頸:精度與規(guī)模化的兼得面臨挑戰(zhàn)

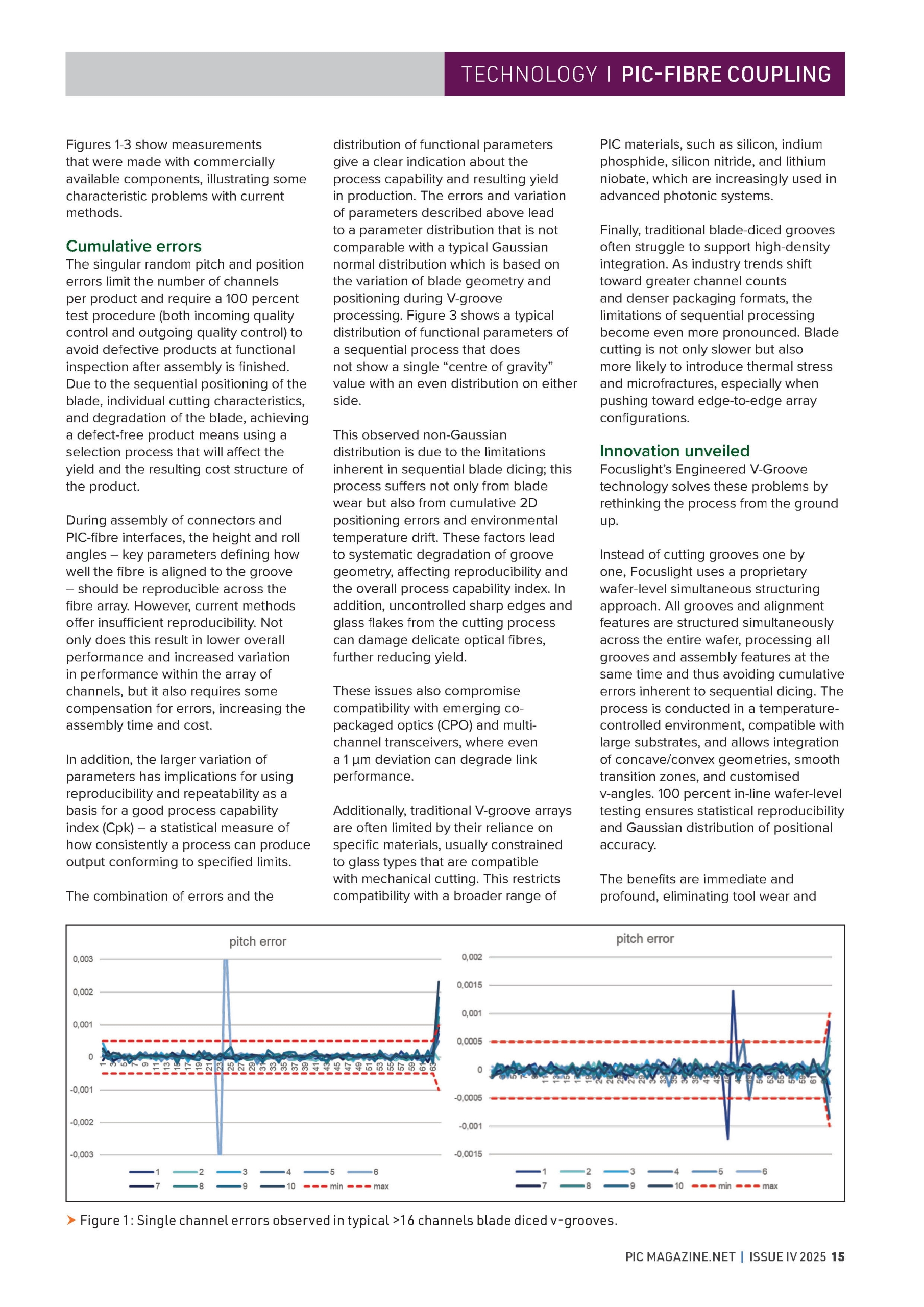

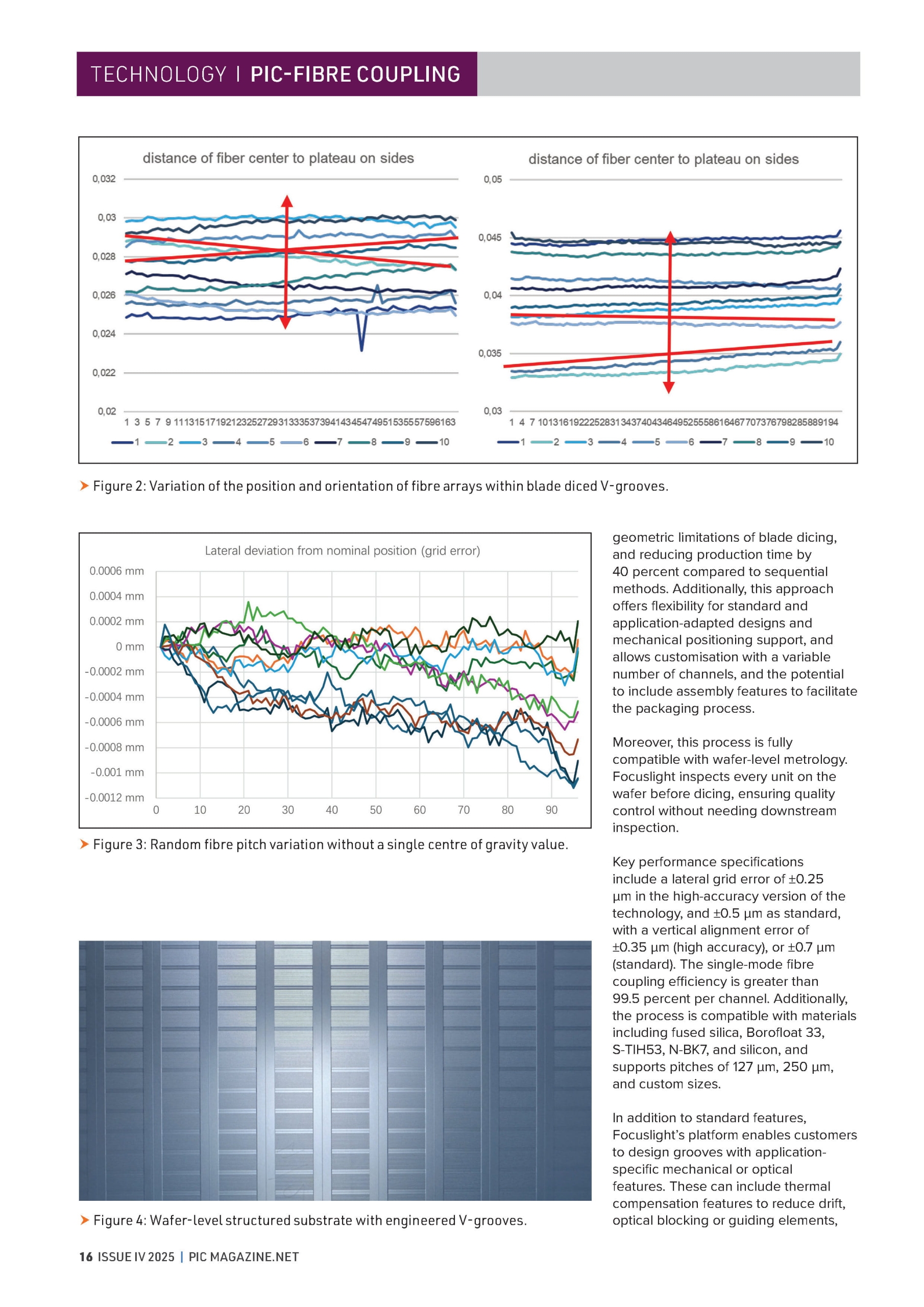

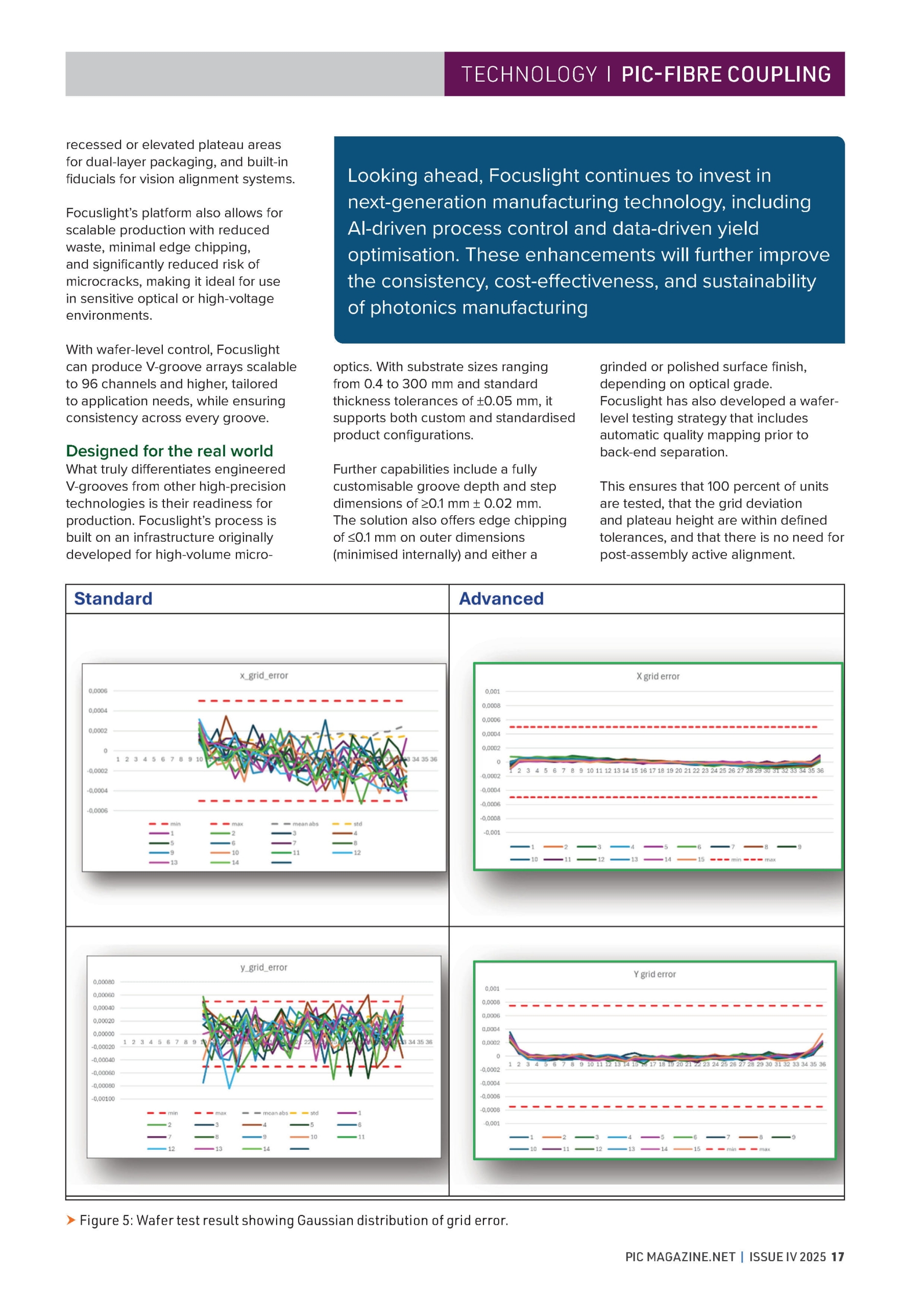

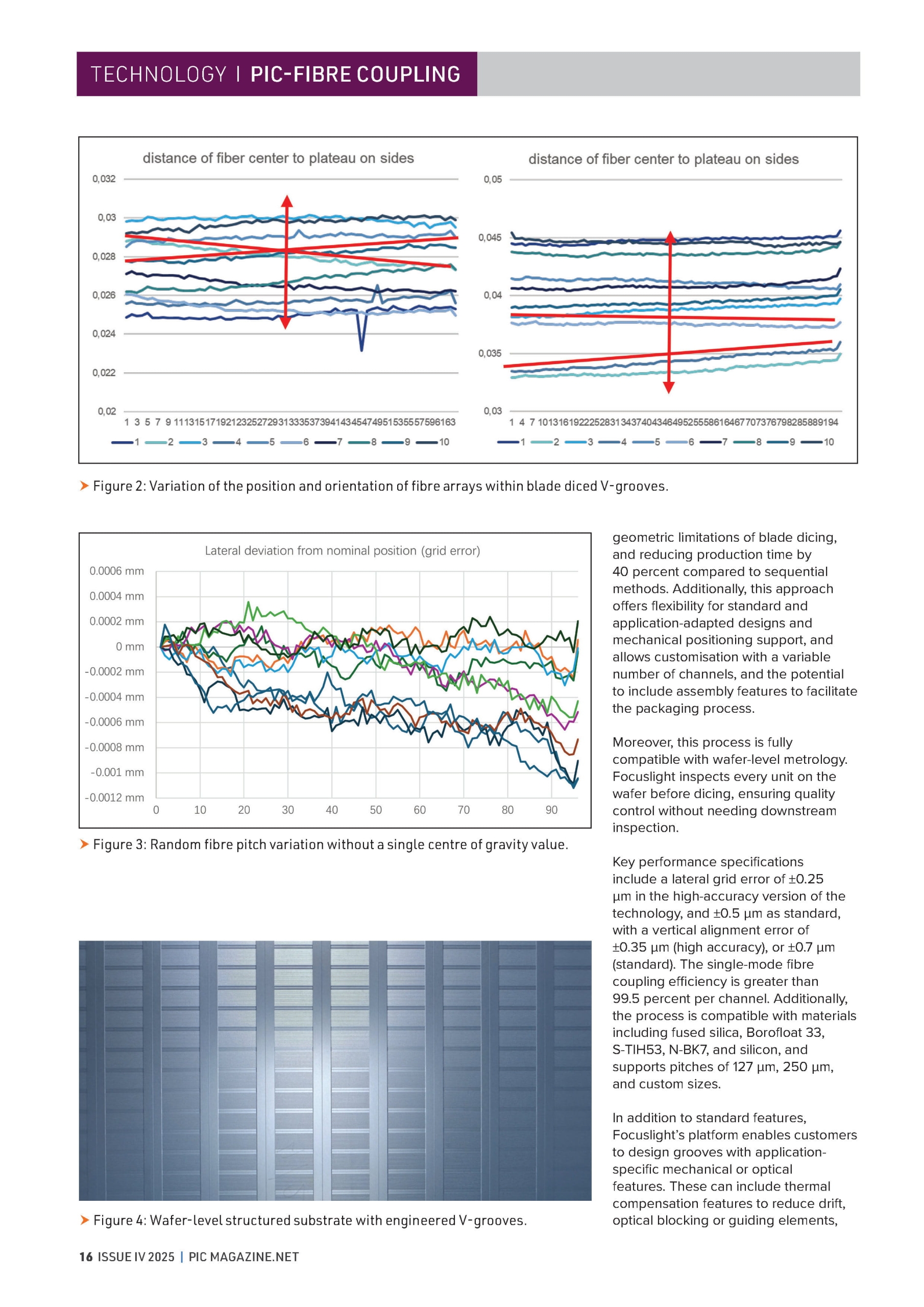

在數(shù)據(jù)中心與AI計(jì)算等領(lǐng)域中,PIC光纖接口的耦合精度與一致性正成為影響其性能與量產(chǎn)能力的核心難題,而傳統(tǒng)V型槽工藝逐槽加工的特點(diǎn),難以同時(shí)滿足亞微米精度與高通道數(shù)量產(chǎn)要求,尤其在面對(duì)CPO等高密度架構(gòu)時(shí),局限性尤為突出。

晶圓級(jí)同步結(jié)構(gòu)化V型槽技術(shù)實(shí)現(xiàn)結(jié)構(gòu)性突破

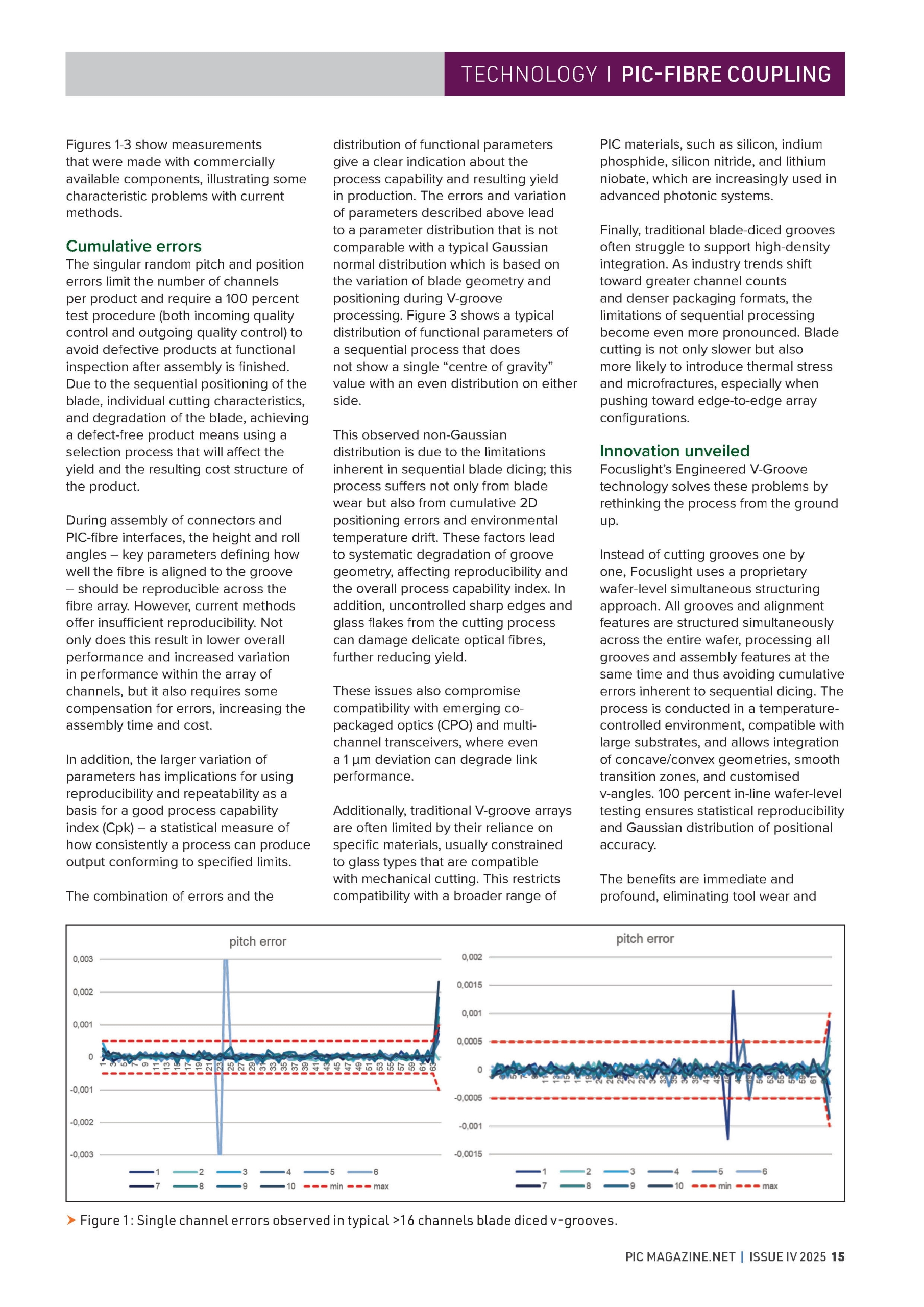

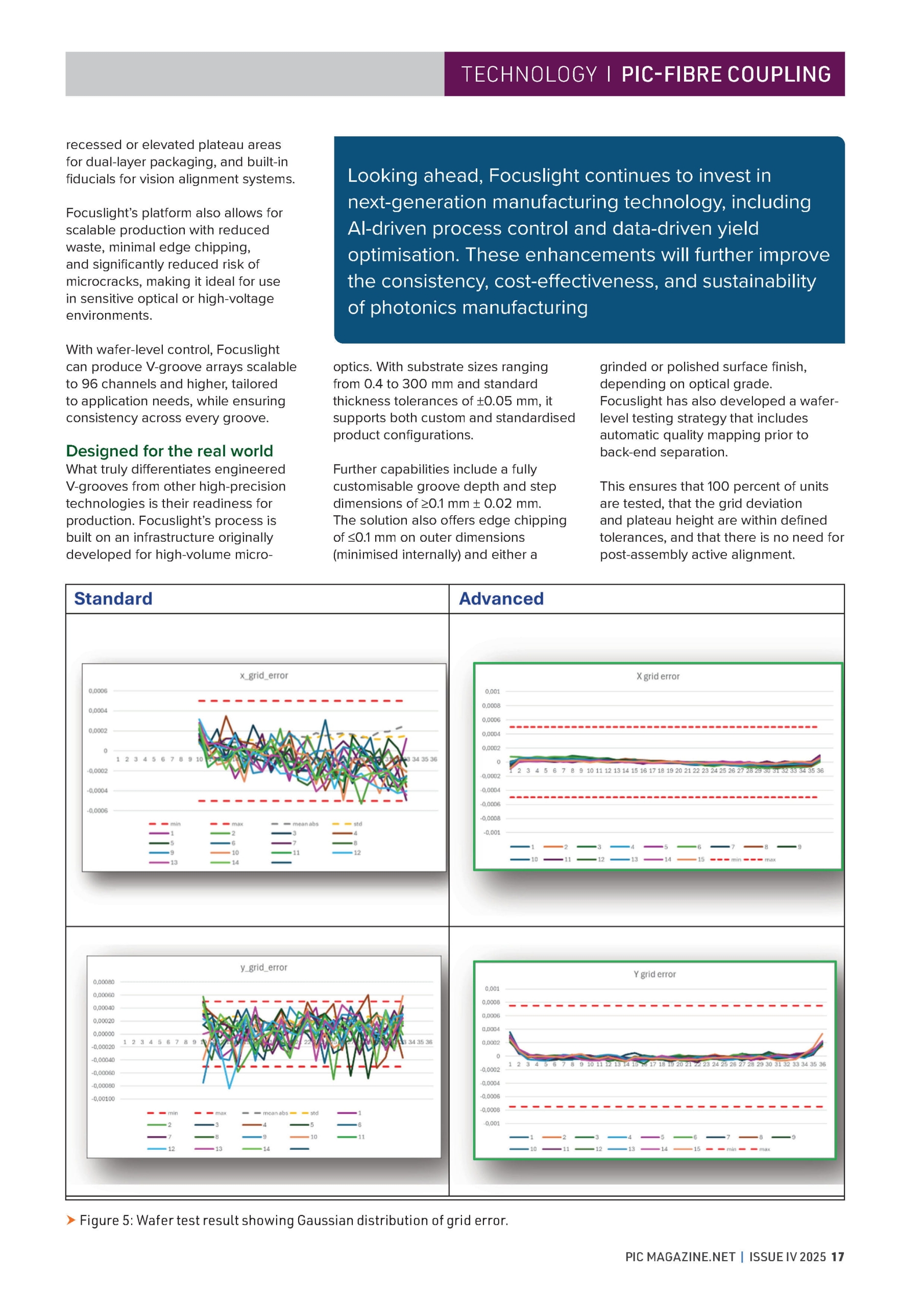

晶圓級(jí)同步結(jié)構(gòu)化工藝基于成熟的晶圓級(jí)生產(chǎn)體系,可實(shí)現(xiàn)一次性在同一晶圓上完成加工所有溝槽與對(duì)準(zhǔn)特征,消除逐槽加工帶來(lái)的累積公差,更可設(shè)計(jì)復(fù)雜幾何結(jié)構(gòu),支持高密度陣列設(shè)計(jì),為高精度和大規(guī)模的光封裝提供了創(chuàng)新性解決方案。

面向CPO應(yīng)用與AI時(shí)代的未來(lái)

晶圓級(jí)同步結(jié)構(gòu)化技術(shù)在保持高良率、高一致性、兼容自動(dòng)化裝配的同時(shí),可支持多達(dá)96通道及以上的陣列設(shè)計(jì),并可選多種材料,為CPO(共封裝光學(xué))、AI計(jì)算及量子通信等高速互聯(lián)應(yīng)用提供可靠支持。秉承“歐洲精工,亞洲智造——加速高精度微光學(xué)全球布局”的理念,炬光科技持續(xù)推動(dòng)晶圓級(jí)高精度微納光學(xué)技術(shù)在光通信領(lǐng)域的規(guī)模化應(yīng)用,為高密度、高性能光通信系統(tǒng)奠定制造基礎(chǔ)。

- 全文轉(zhuǎn)載如下 -

溫馨提示:請(qǐng)點(diǎn)擊下圖放大瀏覽或點(diǎn)擊文末“原文鏈接”查看電子版雜志(原鏈接加載時(shí)間較長(zhǎng),請(qǐng)耐心等待)。

以上完整文章轉(zhuǎn)載自《PIC Magazine》2025年冬季刊第14-18頁(yè)。

原文鏈接:https://picmagazine.net/article/123069/Reimagining_PIC-fibre_interfaces_with_engineered_V-Groove_technology

返回

返回